Elektronischer Speicher

Allgemein

Als elektronische Speichermedien werden Speicher bezeichnet, die Daten auf oder auf Basis von elektronischen Halbleiterbausteinen speichern.

Vor allem für den Endnutzer erhältlichen Halbleiterspeicher, werden oft als kombiniertes Produkt mit integriertem Controller hergestellt. Damit bilden sie einen integrierten Schaltkreis (IC_) beziehungsweiße einen Teil desselben, meist als „eingebetteter Speicher“ zu bezeichnen.

Klassen von Halbleiterspeichern

nach Art der Datenhaltung

Ein gängiges Kriterium zur Klassifizierung von Halbleiterspeichern, sind die Arten der Datenhaltung:

Datenhaltung |

änderbar |

Beispiel |

Nutzungsgründe |

Nutzungsbeispiele |

|---|---|---|---|---|

flüchtig |

ja |

RAM |

schnell |

Arbeitsspeicher, Cache |

permanent |

nein |

ROM |

persistent, unveränderbar |

Betriebssystem, Firmware |

semi-permanent |

ja |

Flash-Speicher |

persistent, veränderbar |

USB-Sticks, SD-Karten, SSDs |

flüchtiger Speicher

Flüchtige Halbleiterspeicher verlieren ihren Speicherinhalt, sobald die Energieversorgung ausgeschaltet wird. Eine dauerhafte Speicherung ist nur mit unterbrechungsfreien Stromversorgung möglich. Da sie besonders schnell sind und damit gut als Arbeitsspeicher geeignet sind, werden sie dennoch aktiv genutzt.

- RAM

Random Access Memory – (wahlfreier Zugriff)

- DRAM

Dynamic Random Access Memory

- SRAM

Static Random Access Memory

permanenter Speicher

Permanente Halbleiterspeicher sind nicht neu programmierbar oder beschreibbar. Ihr Speicherinhalt ist dauerhaft unveränderlich. Typischerweise enthalten permanente Halbleiterspeicher Betriebssysteme, Anwendungsprogramme und Firmware an denen während des Betriebs keine Änderungen vorgenommen werden müssen. In der Regel werden ROM- und PROM-Bausteine austauschbar auf der Platine befestigt.

- ROM

Read Only Memory – (nur lesender Zugriff)

- PROM

Programmable ROM

Heute dient meist Flash-Speicher als EPROM- und EEPROM-Ersatz.

semi-permanenter Speicher

Semi-permanente Halbleiterspeicher sind digitale Festwertspeicher, die wiederholt neu programmiert werden können.

- EPROM

Erasable Programmable ROM – (lesend und schreibend)

- EEPROM

Electrically Erasable Programmable ROM

- Flash-Speicher

Flash-EEPROM – (blockweise gleichzeitig)

- FRAM

Ferroelectric RAM

- MRAM

Magnetoresistive RAM

- PCRAM

Phase Change RAM

- RRAM / ReRAM

Resistive RAM

Heute dient meist Flash-Speicher als ROM- und PROM-Ersatz.

nach Art des Speicherzugriffs

Alternativ können Halbleiterspeicher zum Beispiel auch nach der Art des Speicherzugriffs klassifiziert werden.

Technik

Einige Beispiele zur technischen Funktionsweiße von elektrischen Speichermedien:

flüchtiger Speicher

RAM

Zu RAM Arbeitsspeichern zählen alle Schreib-Lese-Speicher mit wahlfreiem Zugriff.

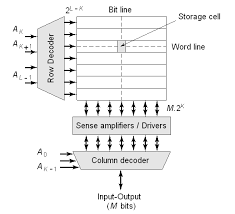

Die Speicherzellen sind in einer zweidimensionalen Matrix angeordnet. Mit dem Kreuzungspunkt des Reihen- und Spaltenzählers als eindeutige Adresse, sind sie gezielt ansprechbar. Der Speicherzustand jeder so ausgewählten Zelle kann beliebig oft gelesen oder verändert werden. Ein Ausfall der Betriebsspannung löscht alle im RAM gespeicherten Informationen.

SRAM

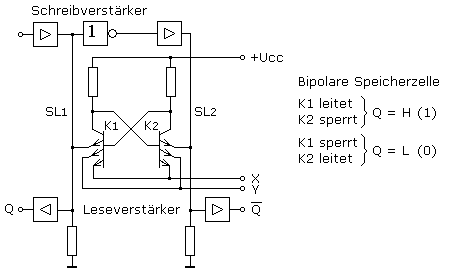

SRAM speichert den jeweiligen Binärwert in einem Flipflop, welches in bipolarer TTL- und ECL-Technik sowie mit MOS-Feldeffekttransistoren hergestellt werden kann.

- Bipolare Transistortechnik

Prinzipschaltung in TTL-Technik für eine Flipflop Speicherzelle:

- Aktivierung

Die Speicherzelle wird durch eine anliegende Betriebsspannung aktiviert. Der Emitterstrom des leitenden Transistors kann nur noch über seine Schreib-Lese-Leitung fließen.

- Lesevorgang

Bei einem in der Zelle gespeicherten Binärwert 1 ist der Transistor K2 gesperrt und K1 leitend.

Aktivierung

Transistor K1 frei / Transistor K2 gesperrt

Strom fließt durch SL1 / SL2 bleibt stromlos

Q hat High Pegel -> Speicherzustand 1 / Q-Nicht hat Low Pegel

Bei einem in der Zelle gespeicherten Binärwert 0 ist der Transistor K1 gesperrt und K2 leitend.

Aktivierung

Transistor K2 frei / Transistor K1 gesperrt

Strom fließt durch SL2 / SL1 bleibt stromlos

Q hat Low Pegel -> Speicherzustand 0 / Q-Nicht hat High Pegel

Schreibvorgang

Aktivierung

High Pegel an SL1 & Low Pegel an SL2

sperrt K1 & schaltet K2 frei -> Speicherzustand 0

Aktivierung

Low Pegel an SL1 & High Pegel an SL2

sperrt K2 & schaltet K1 frei -> Speicherzustand 1

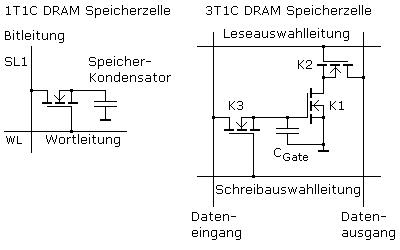

DRAM

DRAM speichert die Information als Kondensatorladungen. Ein aufgeladener Kondensator entspricht der logischen 1, ein entladener Kondensator der logischen 0. Einer oder mehrere Transistoren schalten den Kondensator an die Schreib-Lese-Leitungen.

Die Aktivierung der Zeile erfolgt mit dem „row address strobe“ RAS-Signal gefolgt von der Spaltenadresse, dem „column address strobe“ CAS-Signal zum Auslesen der gespeicherten Zustände.

Für den Lese- und Schreibvorgang gibt es getrennte Auswahl- und Datenleitungen.

- Leseprozess

Bei einem in der Zelle gespeicherten Binärwert 1 ist das Gate des Transistor K1 positiv geladen:

High Pegel an Datenausgangsleitung

gleicht den Einfluss der unterschiedlichen Leitungskapazitäten aus

positiver Spannung an Leseauswahlleitung

Transistor K2 leitend

positives Potenzial am Drain des Speichertransistors K1

K1 leitet

zieht das Potenzial der Datenausgangsleitung

invertierter Datenausgangspegel -> Speicherzustand 1

Bei einem in der Zelle gespeicherten Binärwert 0 ist das Gate des Transistor K1 nicht geladen:

High Pegel an Datenausgangsleitung

gleicht den Einfluss der unterschiedlichen Leitungskapazitäten aus

positiver Spannung an Leseauswahlleitung

Transistor K2 leitend

positives Potenzial am Drain des Speichertransistors K1

K1 gesperrt

Datenleitung behält High Pegel

invertierter Datenausgangspegel -> Speicherzustand 0

- Schreibprozess

In die Zelle soll eine logische 1 geschrieben werden:

High Pegel an Dateneingang

High Pegel an der Schreibauswahlleitung

Transistor K3 leitend

lädt die Gatekapazität von K1 positiv auf

Low Pegel an Schreibauswahlleitung

Transistor K3 gesperrt -> Speicherzustand 1

Da auch MOS-Transistoren im Sperrzustand keine idealen Nichtleiter sind, muss der Ladezustand des Speicherkondensators regelmäßig aufgefrischt werden.

- Burst-Refresh:

Der Refresh erfolgt für alle Speicherzellen gleichzeitig. Der normale Speicherbetrieb ist um 40 µs relativ lange unterbrochen.

- Cycle-Stealing:

Der Refresh erfolgt verteilt nacheinander auf jeweils nur eine Zeilenadresse. Durch ein WAIT-Signal gesteuert ist der normale Zugriff bei 128 Zeilen nur noch für rund 300 ns unterbrochen.

- Hidden-Refresh:

Der Refresh ist so auf den Prozessortakt synchronisiert und erfolgt nur, wenn dieser keine Speicherzugriffe ausführt. Die Speicherbausteine werden als (synchrone) SDRAM bezeichnet.

Festwertspeicher

permanenter Speicher

ROM

Festwertspeicher mit wahlfreiem Zugriff sind vom Hersteller vorprogrammiert oder vom Nutzer einmalig programmierbar. Die gespeicherten logischen Zustände lassen sich beliebig oft lesen.

- Schreibprozess durch Maskenprogrammierung

Eine aufgelegte Maske bestimmt beim Ätzprozess, wo aktive Koppelelemente zwischen den Wort- und Bitleitungen entstehen und wo sie fehlen.

Maskenprogrammierung ist für kleinere Stückzahlen und spezielle Anwendungen nicht rentabel.

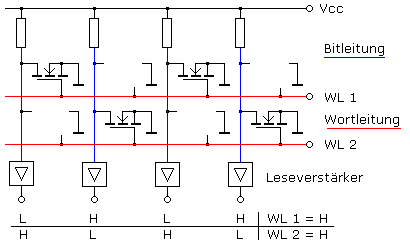

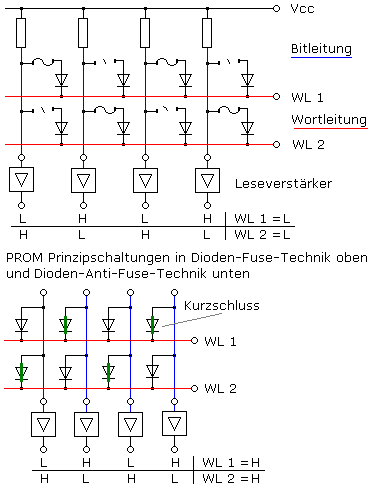

PROM – Programmierbare Festwertspeicher

PROM sind einmalig programmierbar und arbeiten danach als ROM.

Die Zellen sind als Dioden- oder Transistormatrix aufgebaut, deren Verbindungspunkte bei der Programmierung nicht umkehrbar hochohmig oder niederohmig zerstört werden.

In einer Variante ist jedes Zellenelement mit einem sehr dünnen Chrom-Nickel-Sicherungsdraht verbunden, der bei der Programmierung überlastet und hochohmig zerstört wird.

In einer anderen Variante führt ein Spannungsimpuls auf der jeweiligen Bitleitung zum Kurzschluss der Diode.

semi-permanenter Speicher

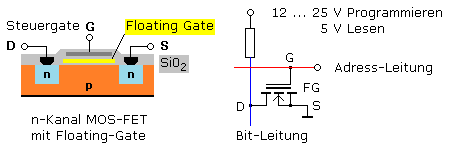

EPROM Festwertspeicher

EPROM-Speichertransistoren haben ein zusätzliches vollkommen isoliertes „Floating-Gate“, welches mit seiner elektrischen Ladung den Speicherzustand der Zelle bestimmt. Nach der Herstellung und im gelöschten Zustand ist das Floating-Gate ladungsneutral. Es ist mit energiereicher UV-C Strahlung komplett löschbar und kann danach neu programmiert werden.

Leseverfahren

Niedrige Spannung an Adressleitung, die den Transistor mit dem negativ geladenen Floating-Gate nicht mehr leitend schalten kann

Das Potenzial auf der Bitleitung wird nicht nach Masse gezogen und bleibt auf High Pegel. -> Speicherzustand 1

Niedrige Spannung an Adressleitung, die den Transistor mit dem negativ geladenen Floating-Gate nicht mehr leitend schalten kann

Eine Zelle mit nicht geladenem Floating-Gate leitet und die Bitleitung wechselt auf Low Pegel. -> Speicherzustand 0

Schreibprozess (Programmierung nach dem HCI-Verfahren)

Hohe Spannung, welche Elektronen stark beschleunigt (hot electrons)

Diese können sowohl die Energiebarriere zum Leitungsband überwinden als auch durch Stoßionisation weitere Ladungsträgerpaare erzeugen.

Energiereiche Elektronen aus diesem Lawineneffekt (Avalanche-Effekt) gelangen in das Leitungsband, wodurch dieses negativ aufgeladen wird.

Die Ladung bleibt nach dem Abschalten der Programmierspannung erhalten. -> Speicherzustand 1

Löschverfahren

Mit kurzwelliger, energiereicher Strahlung kann sich das Floating-Gate entladen. Die energiereichen Photonen erzeugen in der Isolierschicht Elektronen-Lochpaare und die im Floating-Gate gespeicherte Ladung kann bei anliegender Spannung abfließen.

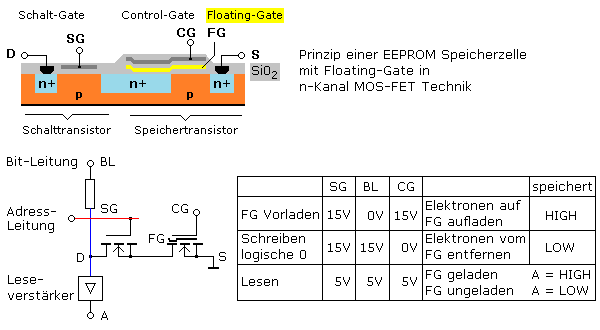

EEPROM Festwertspeicher

Das Programmieren und Löschen erfolgt ohne externes Programmiergerät in der Einsatzschaltung. Die Ladungsverschiebung auf das Floating-Gate erfolgt nach einem von Fowler und Nordheim mathematisch beschriebenen quantenmechanischen Tunneleffekt.

Leseverfahren

normale niedrige Betriebsspannung an Wort- und Bitleitung

Schalttransistor leitend

selbe Spannung an Control-Gate

Ist das Floating-Gate negativ geladen, so bleibt der Transistor gesperrt und die Spannung auf der Bitleitung hoch.

Der Leseverstärker gibt High Pegel aus. -> Speicherzustand 1

Mit dem Anlegen der normaler niedriger Betriebsspannung an die Wort- und Bitleitung wird der Schalttransistor leitend.

Mit ebenfalls 5 V am Control-Gate wird der Speicherzustand gelesen.

Ist keine Ladung auf dem FG gespeichert, dann wird der Transistor leitend geschaltet und zieht die Spannung der Bitleitung nach Masse

Der Leseverstärker gibt Low Pegel aus. -> Speicherzustand 0

Schreibprozess (Programmierung)

Grundzustand: Geladenes Floating-Gate

Programmierspannung an Adressleitung mit dem Gate des Schalttransistors und das Steuergate CG des Speichertransistors

Schalttransistor leitet

Programmierspannung an CG verursacht Tunneleffekt und zieht Elektronen aus dem Drainbereich auf das Floating-Gate

Floating-Gate speichert negative Ladung und erhöht damit das Potenzial zwischen Gate und Source

Speichertransistor wird leitend geschalten -> Speicherzustand 1

Löschverfahren

Das Floating-Gate kann entladen und somit umprogrammiert werden, wenn an der Adress- und Bitleitung die Programmierspannung anliegt und das Control-Gate Massepotenzial hat.

Der Schalttransistor leitet und die Drainspannung unter dem FG ist gleich der Programmierspannung. Der Speichertransistor bleibt mit CG = 0 V gesperrt.

Die vom Drain ausgehende hohe Feldstärke zieht mit dem Tunneleffekt die negative Ladung vom FG ab.

NAND- vs. NOR-Flash

Die NAND- und NOR-Architekturen unterscheiden sich grob gesehen in der Speicherdichte und der Zugriffsgeschwindigkeit.

NOR-Flash

NOR-Flash [Elektronik-Kompendium]

Speicherzellen parallel verschaltet

geringeren Widerstand zwischen Stromquelle und Auswerteschaltung

wahlfreier und direkter Zugriff -> kurze Zugriffszeiten

Nutzung: Programmspeicher von Mikrocontrollern (z.B. als nichtflüchtiger Speicher für das BIOS)

NAND-Flash

NAND-Flash [Elektronik-Kompendium]

Speicherzellen intern seriell verschaltet -> Lesen und Schreiben nur in Blöcken möglich

geringe Anzahl an Datenleitungen -> weniger Platz

Nutzung: Massenspeicher, wie Speicherkarten, USB-Sticks und SSDs (geeignet, da diese blockweise lesen)

Vergleich zu anderen nichtflüchtigen Speicherarten:

höhere Speicherdichte zu geringen Kosten

schnelle Schreibgeschwindigkeit

geringer Stromverbrauch